FM4,5,6 チャンネルとリズム音源、ADPCM 音源を使う場合に以下の I/O ポート $46-$47 を使います。$A8-$A9,$AA 側は適宜読み替えのこと。

| I/O ポート $46 【入力】 | ||

|---|---|---|

| bit | 7 | [BUSY]1=データをレジスタにセット中 |

| bit | 6 | 未使用 |

| bit | 5 | [PCMBSY] 1=ADPCM録音・再生中 |

| bit | 4 | [ZERO] 1=ADPCM録音中に無音状態になった |

| bit | 3 | [BRDY] 1=ADPCM録音・再生またはメモリへの格納が 1byte 完了した |

| bit | 2 | [EOS] 1=ADPCM録音・再生が終端アドレスに達した、またはPCM再生周期になった |

| bit | 1 | [FLAGB]1=OPNA タイマー B がオーバーフローした |

| bit | 0 | [FLAGA]1=OPNA タイマー A がオーバーフローした |

| I/O ポート $46 【出力】 | ||

|---|---|---|

| bit | 7-6 | OPNA レジスタ指定 |

| I/O ポート $47 【入出力】 | ||

|---|---|---|

| bit | 7-6 | OPNA データ入出力 |

$47 の入力で読めるのは ADPCM 部のデータだけです。録音やデータ読み出しなどで ADPCM レジスタ $8,$F からの入力が必要になります。

OPN の $44,$45 と役割はほぼ同じですが、ステータス部分に ADPCM 関係のものが増えています。

BUSY は $44 にもありますが、$46 は FM4,5,6 ・リズム音源用の BUSY です。

FM1,2,3 の BUSYは変わらず $44 側です。

FLAG A/B については $44 側にも同じものがあります。両方で共通の値を読むことが出来ます。

新設されたフラグも含めて、OPNA レジスタ $29 が割り込み関連のコントロールポートになっています。

タイマ A/B の設定は OPN の $27 にもあるので、FM4-6, ADPCM を有効にするついでに、こちらも有効にしておきましょう。

| OPNA レジスタ $29 【出力】 | ||

|---|---|---|

| bit | 7 | 1=FM4-6, ADPCM を使用可能にする |

| bit | 4 | 1=ADPCM録音中に無音状態になった時に[ZERO]フラグを立て割り込みをかける |

| bit | 3 | 1=ADPCM録音・再生またはメモリへの格納が 1byte 完了したときに[BRDY]フラグを立て割り込みをかける |

| bit | 2 | 1=ADPCM録音・再生が終端アドレスに達した、またはPCM再生周期になった時に[EOS]フラグを立て割り込みをかける |

| bit | 1 | 1=OPNA タイマー B がオーバーフローしたときに[FLAGB]を立て割り込みをかける |

| bit | 0 | 1=OPNA タイマー A がオーバーフローしたときに[FLAGA]を立て割り込みをかける |

[ZERO][BRDY][EOS] については新しく割り込みトリガになりました。

後述する PCM 再生処理などに対して役に立つのですが、エミュレータでは省略されていることがあります。

OPN においてタイマ A/B がオーバーフローしたときに、これをクリアする必要がありましたが、OPNA における新設フラグ群も同様です。

| OPNA レジスタ $10 【出力】 | ||

|---|---|---|

| bit | 7 | 1=全フラグを 0 にする。bit4-0 の設定は無視 |

| bit | 4 | 1=[ZERO]を常に 0 にマスクする |

| bit | 3 | 1=[BRDY]を常に 0 にマスクする |

| bit | 2 | 1=[EOS]を常に 0 にマスクする |

| bit | 1 | 1=[FLAGB]を常に 0 にマスクする |

| bit | 0 | 1=[FLAGA]を常に 0 にマスクする |

ADPCM 関連の割り込みを使用した後は、レジスタ $10 に $80 を出力してフラグをクリアします。

レジスタ指定後にデータが書き込めるようになるまでのウェイトは OPN よりも減っており、

CPU が 4MHz なら 9 クロック、8MHz なら 17 クロックです。安全のため 8MHz-H に合わせておきましょう。

MA2 までなら実質 6MHz 程度なので割とルーズでも大丈夫なのですが。

このウェイトは FM 音源部とリズム音源部で必要です。PSG と ADPCM は必要無し。

WriteOPNA:

in a,($44)

rlca

jr c,WriteOPNA

ld a,d

out ($44),a

nop ;dummy

ld a,e

out ($45),a

ret

|

FM 音源部のデータ書き込み後のウェイトはレジスタ $21-$9E(音色パラメータ)で 83 クロック、$A0-$B6(BLK/FNUM など)で 47 クロックとか。

ADPCM 部への書き込みは PSG と同様、データ書き込み後も含めノーウェイトです。

注意すべきはリズム音源で、$10 のキーオン・ダンプに 576 クロックのウェイト、それ以外に 83 クロックのウェイトが掛かります。

いずれにせよ、ここは busy フラグを見てウェイトを取るべきでしょう。

ウェイトを嫌ってか(あるいは貧弱なリズム音を嫌ってか)リズム音源を使わないメーカーもありました。

ADPCM 部についての豆知識。

- リミットアドレスは起動直後 $0000 になっている。

- リミットアドレスは必須では無い。$1FFF を一度書き込んでおけば、毎回書き込む必要はない。

- ストップアドレスは ADPCM 録再の場合はあったほうが良いが、こちらも必須では無い。単に EOS フラグのためだけに見ている。

- フラグリセットや DRAM 種別もメモリの読み書きだけなら一度で良い。

- 資料にはストップアドレス+1 を書き込むよう注意書きがあるが、これが必要なのは「読み出し」のみ。

- メモリ読み書き完了後の、レジスタ $00.bit0 へのリセットは必須。これが無いと次の読み書き時にスタートアドレスを書き込んでも無効になる。

- メモリ読み書き前に、レジスタ $00.bit5 のメモリアクセス許可は必須。

- 上記「リセット」と「メモリアクセス許可」は同時にはできない。

- メモリを 1byte 読み書きする毎に BRDY をチェックする必要はない。従ってフラグのリセット $10.bit7 も必要ない。

- x8 モードでのメモリの読み書きは 32byte 単位で行う必要は無く、$00.bit0 でリセットをかけて途中で打ち切っても良い。

- ADPCM はきちんと停止(リセット)しないと次の再生ができない。

- ADPCM 再生中のリアルタイム Delta-N(再生レート)変更は可能。

- ADPCM 再生中のリアルタイム音量変更は可能。

- ADPCM 再生中のリアルタイム定位変更は可能。

一例としてメモリから読み出しを掲載します。書き込みもほぼ同様です。

※ 以下、8MHz-S までは大丈夫ですが、8MHz-H だと化けるようなので、素直にウェイトを取った方がいいかも。

ADPCM_Init: ;初回に一度だけ呼び出せばよい

ld c,$46

ld de,$1000 ;フラグコントロール どのフラグもマスクしない

call WriteFM2

ld de,$1080 ;フラグコントロール 全てのステータスフラグを0に

call WriteFM2

ld de,$0102 ;x8 DRAM

call WriteFM2

ld de,$04FF ;ストップアドレス下位 $04

call WriteFM2

ld de,$051F ;ストップアドレス上位 $05

call WriteFM2

ld de,$0CFF ;リミットアドレス下位 $FF

call WriteFM2

ld de,$0D1F ;リミットアドレス上位 $1F

jp WriteFM2

ADPCM_READ2:

ld c,$46

ld de,$0020 ;$00 メモリアクセス許可

call WriteFM2

ld hl,(ADPCM_START)

ld d,$02

ld e,l ;$02 スタートアドレス下位

call WriteFM2

ld d,$03

ld e,h ;$03 スタートアドレス上位

call WriteFM2

ex de,hl

ld hl,(ADPCM_END)

or a

sbc hl,de ;Length=End-Start+1

inc l ;+1はdec hlと相殺

inc h

ex de,hl

ld a,$08

out (c),a

inc c

in a,(c)

in a,(c) ;2回分空読みする

ld hl,(ADPCM_ADR) ;書き込み先

.loop:

ld b,32

inir ;BRDY を見る必要なし. フラグのリセットも必要なし.

dec e

jp nz,.loop

dec d

jp nz,.loop

dec c

ld de,$0001 ;$00 コントロール1 リセット

jp WriteFM2

|

ADPCM の操作がノーウェイトといっても毎回手間をかけるのはやはり無駄なので、できるだけ速いほうが良いでしょう。

PC88 における YM-2608 の利用は ADPCM として使用されることがほとんどでしたが、PC98 における 86PCM と同様に PCM 録音・再生も可能です。

PCM を録音・再生する場合はボード上に載った 256KB メモリではなく本体メモリと Z80 CPU からの逐次書き込みが必要です。

ADPCM の場合と比べて、かなり CPU パワーとメモリを使うので、確かに PC88 向きではありません。

データは符号付き 8bit を ADPCM のレジスタ $0E に書き込む(録音は $0F から読み込む)だけです。音量は指定できません。

録音・再生周波数は EOS をポーリングするか、EOS を元に割り込みをかけるかの二通りあります。

EOS は ADPCM のプリスケール設定に周波数値を与えると、その周期でフラグが立ちます(あるいは割り込みがかかる)。

前掲の OPNA レジスタ $29 に割り込みソースとして EOS を選択できるようになっているのでこれを使うのがスマートだと思います。

もちろん、フラグを一切使わずに、CPU でタイミングをとるやり方でも録音・再生はできます。

EOS 割り込みは、8MHz ÷ 2 ÷ PreScale(11bit) という式なので、1950Hz 〜 4MHz の割り込みができます。

他のタイマーリソースと比べても、結構こまかく使えて便利だと思います。ただしエミュレータではサポートされていないことも。

Timer A/B も併用しているのであれば、I/O ポート $44/$46 を割り込み時に読んでみて、どの割り込みが発生したかの場合分けが必要です。

また、割り込みが発生する度にフラグクリアも必要ですが、ZERO,BRDY,EOS の 3 つは Timer-A/B と違い、

個別にリセットがかけられないので注意が必要です。逆にオールリセット(Reg.$10=$80)を使うと Timer-A/B もクリアされてしまいます。

こうしてみると、ADPCM と比べて PCM を使うメリットは皆無に思えてきますが、PCM でしか出来ないこともあります。

例えば PCM の多重再生や PCM のリアルタイム合成です。

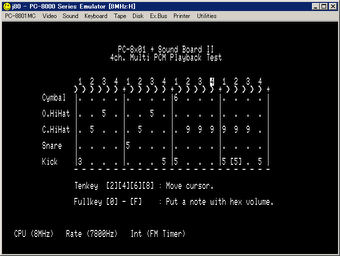

PCM 再生テストを兼ねて、多重再生のデモを置いておきます(-> rhythm_box)。

EOS 割り込みが使えないので、エミュレータの方は Timer-A で代用してあります。

ただし PCM 機能そのものが省略されているエミュレータでは動きません。

8MHz(H) であっても音が時々飛びます。

音を 2 つに限定するなり音量調節を諦めるなりすれば、その分音質や CPU パワーが削減できます。

15600Hz で ADPCM 最高音質と同じになります。

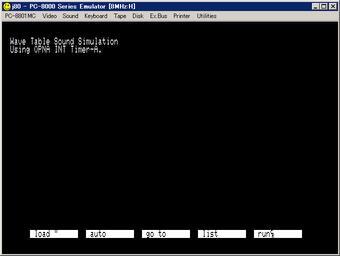

PCM のリアルタイム合成のデモとして波形メモリ音源を PCM でつくってみました(-> wtsnd)。

8bit 32step の波形に音程と音量の変更可、チャンネル数は 2 で 10400Hz のサンプリングレートという仮想スペックです。

コンセプトの実証が主目的なので実装がいいかげんなのは大目に見てください。

このデモは CPU 8MHz モードでのみ動作します。